CSE 1325 Final Assessment Summer 2021 PDF

| Title | CSE 1325 Final Assessment Summer 2021 |

|---|---|

| Course | Digital Logic Design |

| Institution | United International University |

| Pages | 2 |

| File Size | 77.9 KB |

| File Type | |

| Total Downloads | 7 |

| Total Views | 135 |

Summary

Digital Logic Design Theory - Semester Final Question - Summer 2021...

Description

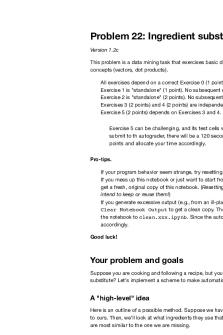

United International University Department of Computer Science and Engineering CSE 1325: Digital Logic Design, Final Assessment, Summer 2021 Total Marks: 25 Time: 1 hour 15 minutes + 15 minutes (for uploading) “Any examinee found adopting unfair means will be expelled from the trimester / program as per UIU disciplinary rules.” Answer all of the questions from 1 to 5 1. The state diagram for recognizing a particular sequence of bits is given below:

i) Identify and write the sequence that’s being recognized. Suppose an input bit stream “01110111110” is given to this system. What will be the output stream?

[1]

iii) Complete the design of this sequence recognizer using D Flip flops by drawing the state table with Flip-flop’s excitation inputs.

[3]

(b) Show the K-map minimization of input and output functions.

[2]

2. Design a 3 bit synchronous up-down counter with two control bits C and D. The circuit counts up when the control variable C = 1 and counts down when C = 0. Also, the circuit will work if D = 1 and remains unchanged if D = 0. You can’t use more than three negative edge triggered JK Flip flops. Only draw the logic diagram with appropriate labels

[5]

3. Design a function that will take a 3 bit binary number as input and the output will be “HIGH” if total number of 1s in input is less than or equal to total number of 0s and “LOW” otherwise. Now implement this fucntion with 2x1 MUX. You can use more than one 2x1 MUX if necessary but you can’t use any basic gates(AND,OR,XOR,NOT etc). (i) Draw the truth table

[2]

(ii) Draw the logic diagram

[2]

4. a) Design a decimal to excess-3 encoder which can only take 3 bits of input. Derive the truth table and the boolean expression for all the outputs. No need to draw logic diagram. [3]

(b) In a clocked SR NOR latch, why do we use two AND gates in front of the two NOR gates? Give proper reason with a short example.

[2]

5. a) Why JK Flip flop is designed in master-slave fashion? Explain your reason properly with an example diagram. b) Implement the following two functions using 2-to-4 decoders.

[3]

F (A, B) = ΠM (0, 1) X F (X, Y ) = (0, 1) m

(i) Draw the logic diagram with proper symbols. (ii) Can you complete the design with a single decoder? Why or why not?

2

[1] [1]...

Similar Free PDFs

Cse 320 Final Lab Report

- 4 Pages

Calendar Summer A 2021

- 2 Pages

ADM2302 Syllabus-Summer 2021

- 15 Pages

HIN 269 Summer 2021

- 8 Pages

Midterm summer 2021

- 2 Pages

Academic Calendar Summer 2021

- 1 Pages

Summer 2021 Syllabus

- 5 Pages

Schedule - Summer 2021

- 2 Pages

Popular Institutions

- Tinajero National High School - Annex

- Politeknik Caltex Riau

- Yokohama City University

- SGT University

- University of Al-Qadisiyah

- Divine Word College of Vigan

- Techniek College Rotterdam

- Universidade de Santiago

- Universiti Teknologi MARA Cawangan Johor Kampus Pasir Gudang

- Poltekkes Kemenkes Yogyakarta

- Baguio City National High School

- Colegio san marcos

- preparatoria uno

- Centro de Bachillerato Tecnológico Industrial y de Servicios No. 107

- Dalian Maritime University

- Quang Trung Secondary School

- Colegio Tecnológico en Informática

- Corporación Regional de Educación Superior

- Grupo CEDVA

- Dar Al Uloom University

- Centro de Estudios Preuniversitarios de la Universidad Nacional de Ingeniería

- 上智大学

- Aakash International School, Nuna Majara

- San Felipe Neri Catholic School

- Kang Chiao International School - New Taipei City

- Misamis Occidental National High School

- Institución Educativa Escuela Normal Juan Ladrilleros

- Kolehiyo ng Pantukan

- Batanes State College

- Instituto Continental

- Sekolah Menengah Kejuruan Kesehatan Kaltara (Tarakan)

- Colegio de La Inmaculada Concepcion - Cebu