Ee310 sol diode Mechanical Engineering Course Outline PDF

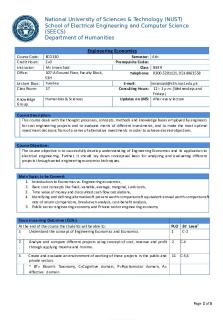

| Title | Ee310 sol diode Mechanical Engineering Course Outline |

|---|---|

| Author | Jeramil Garcia |

| Course | Mechanical engineering |

| Institution | University of Southeastern Philippines |

| Pages | 14 |

| File Size | 857.5 KB |

| File Type | |

| Total Views | 136 |

Summary

Understand the basic operation, construction and characteristics

of different electronic devices such as PN, junction diode, light

emitting diode, Zener diode, Bipolar junction Transistor, Field

Effect Transistor and Operational Amplifier as well as their

application...

Description

EE310 Solved Problems on PN Junction Sedra/Smith 5th/6th ed.

Turki Almadhi, EE Dept., KSU, Riyadh, Saudi Arabia 01/02/43

Guidelines for dealing with circuits that contain diodes to be solved using the ideal diode model: 1. Start with an assumption about the state of each diode in the circuit. In the ideal diode model: a diode could be either turned on (I > 0, where I is in the forward direction) or cut off (V < 0, where V is the voltage of the anode with respect to the cathode). 2. Replace each diode you have assumed to be turned on with a short circuit and each diode you have assumed to be cut off with an open circuit. Solve for the forward currents of all the diodes that you have assumed turned on and the forward voltage drops across all diodes that you have assumed cut off. 3. Verification: Make sure that each and every diode you have assumed to be turned on has I > 0, where I is in the forward direction. Also, make sure that each and every diode you have assumed to be cut off has V < 0, where V is the voltage of the anode with respect to the cathode. 4. If the results of the verification step are consistent with your assumption in step 1 that means you have obtained the correct solution, otherwise you have to try another assumption and restart the process. Guidelines for dealing with circuits that contain diodes to be solved using the constant-voltage-drop model: 1. Start with an assumption about the state of each diode in the circuit. In the constant-voltage-drop model: a diode could be either turned on (I > 0, where I is in the forward direction) or cut off (V < 0.7, where V is the voltage of the anode with respect to the cathode). 2. Replace each diode you have assumed to be turned on with a short circuit and each diode you have assumed to be cut off with an open circuit. Solve for the forward currents of all the diodes that you have assumed turned on and the forward voltage drops across all diodes that you have assumed cut off. 3. Verification: Make sure that each and every diode you have assumed to be turned on has I > 0, where I is in the forward direction. Also, make sure that each and every diode you have assumed to be cut off has V < 0.7, where V is the voltage of the anode with respect to the cathode. 4. If the results of the verification step are consistent with your assumption in step 1 that means you have obtained the correct solution, otherwise you have to try another assumption and restart the process.

Assume that both D1 and D2 are cut off: In that case, I10kΩ = 0 V1 = 5 V ! Also, V2 = 5 – (–5) = 10 V ! but both V1 and V2 must be < 0 our assumption is incorrect. Assume that both D1 and D2 are turned on: In that case, I10kΩ =

(5 – 0)

(10 k)

= 0.5 mA. I2 =

(0 –(−5)) (5 k)

= 1 mA I1 = I10kΩ – I2 = – 0.5 mA !

∵ I1 < 0 which contradicts the condition of a turned-on diode our assumption is incorrect. Assume that D1 is on and D2 is off: In that case, I10kΩ = I1 =

(5 – 0)

(10 k)

= 0.5 mA. V2 = 0 – (–5) = 5 V !

∵ V2 > 0 our assumption is incorrect. Assume that D1 is off and D2 is on: In that case, I10kΩ = I2 =

(5 –(−5)) (15 k)

= (2/3) mA. V1 = [5 – (10 k) × (2/3 m)] – 0 = –1.667 V

∵ V1 < 0 and I2 > 0 that confirms our assumption.

I = I1 = 0; and V = V1 = (5 k) × (2/3 m) + (–5) = –1.667 V

Let us resolve the above problem using a constant voltage drop model with VD = 0.7 V; Assume that both D1 and D2 are cut off: In that case, I10kΩ = 0 V1 = 5 V ! Also, V2 = 5 – (–5) = 10 V ! our assumption is incorrect. Assume that both D1 and D2 are turned on: In that case, I10kΩ =

(5 – 0.7) 10 k

= 0.43 mA. I2 =

∵ I1 < 0 our assumption is incorrect.

(0.7−0.7 –(−5)) 5k

= 1.0 mA I1 = I10kΩ – I2 = – 0.57 mA !

Assume that D1 is on and D2 is off: In that case, I10kΩ = I1 =

5 – 0.7 10 k

= 0.43 mA. V2 = 0.7 – (–5) = 5.7 V !

∵ V2 > 0.7 our assumption is incorrect. Assume that D1 is off and D2 is on: In that case, I10kΩ = I2 =

(5 –0.7−(−5)) 15 k

= 0.62 mA. V1 = [5 – (10 k) × (0.62 m)] – 0 = –1.2 V

∵ V1 < 0.7 and I2 > 0 that confirms our assumption.

I = I1 = 0; and V = (5 k) × (0.62 m) + (–5) = –1.9 V

∵ the three diodes are identical and conduct the same current (I), The voltage drop across each diode will be the same = VD. Now we have 3VD = 2 VD 0.667 V or 667 mV. 667

I = 1×10−14 × 𝑒 1×25.8 1.69 mA If a current of 1 mA is drawn away from the output terminal that leaves the diodes with 0.69 mA. The change in a single diode voltage will be ΔVD = 2.3 × 𝑛 × 𝑉𝑇 × log ΔV = 3 ΔVD = −70 mV

0.69

1.69

= −23.34 𝑚𝑉

i.e., V loaded = V + ΔV = 1930 mV = 1.93 V.

In general,

For this particular problem, AD1 = 10 AD2 IS1 = 10 IS2

𝐼𝑆1

𝐼𝑆2

= 10

Also by inspection I2 = I – I1 = 8 mA. Writing a node equation starting from the cathode of D 2 and going clockwise, V2 − V1 − V = 0 V =V2 − V1 = 60 × log( 2 ×10) mV = 96 mV. 8

50 = 60 × log (

10−𝐼1 𝐼1

×10) log(

10−𝐼1 𝐼1

×10) = 0.8334 100.8334 = 𝐼1 = 5.61 𝑚𝐴

100 𝐼1

− 10

100 𝐼1

= 17 .814

a) V |T 25 V |T 25

10 A

V |T 25

10 A

V |T 25 V |T 25

25 0 ( 2 mV)

V |

620 mV+ ( 50 mV) 570 mV

1 10 3 V | 2.3nVT log( ) 10 10 6 (570 120) mV =690 mV 1mA

b) V |T 25

, I 1 A

V |T 25

1A

V |T 25

1A

V |T 25 V |T 25

V |T 50

1A

25 50 ( 2 mV)

790 mV+50 mV 830 mV because the current is very large!

1 103 V | 2.3nVT log( ) 1 (830 180) mV = 650 mV 1mA

a) I2

V S V 1 1 0.7 1.5 mA R 200

b) V 2 V 1 2.3nV T log(

I3

V S V 2 1 0.72095 1.39525 mA R 200

V 3 V 2 2.3nV T log(

I4

I3 1.39 525 ) 0.72095 0.119 log( ) 0.71721 I2 1.5

V S V 3 1 0.7172 1 1.41395 mA R 200

V 4 V 3 2.3nV T log(

I5

I2 1.5 ) 0.7 0.119 log( ) 0.72095 I1 1

I4 1.41395 ) 0.71721 0.119 log( ) 0.71789 I3 1.39525

V S V 4 1 0.71789 1.41055 mA R 200

VD VD

decade I D

2.3nVT

decade I D

0.12 V/decade @ RT for n = 2

ID (mA) 1 10

VD (V) 0.7 0.7+0.12=0.82

rD

VD 0.12 13.34 I D 10 1 10 3

V D I D r D V DO V DO V D I D r D V DO 0.7 1 103 13.34 0.687 V To calculate VD exactly, we need to find IS : (

IS ID e

ID (mA)

0.5 5 14

VD ) nVT

3

1 10 e

V D nV T ln(

0.6642 0.7831 0.8362

(

0.7 ) 2 0.0258

I 1) IS

1.2835 10

9

A

Difference VD using Piecewise-linear model 0.6937 0.7537 0.8738

(mV) 29.5 -29.4 37.6

Graphical Analysis (Load Line Method):

Example 1:

The diode used in the circuit below has the i-v characteristic shown to the right. Find the the dc operating (bias) point Q.

Example 2

In the given i-v characteristic below, which load line represent the given circuit? Answer: Number 2.

d) I=100 µA DC Equivalent circuit:

Small Signal Equivalent circuit:

rd 1

nVT 1 .0259 259 I1 100 10 6

vo

rd 2

nV T 1 .0259 28.78 I2 0.9 10 3

rd 2 28.78 0.1 V V vi r r 28.78 259 d2 d1

3.107) A young designer, aiming to develop intuition, concerning conducting paths within an integrated circuit, examines the end-to-end resistance of a connecting bar 10 m long, 3 m wide, 1 m thick, made of various materials. The designer considers: a) b) c) d) e)

intrinsic silicon n-doped silicon with ND = 1 × 1016/cm3 n-doped silicon with ND = 1 × 1018/cm3 p-doped silicon with ND = 1 × 1010/cm3 aluminum with resistivity of 2.8 Ωcm

Find the resistance in each case. For intrinsic silicon, use n = 1350 cm2/Vs, p = 480 cm2/Vs, and ni = 1.5 × 1010/cm3. For doped silicon, assume n 2.5p = 1200 cm2/Vs. (Recall that R = L/A.)

In general, 𝑛=

𝑁𝐷 −𝑁𝐴 2

+ √(

𝑎) 𝑛 = 𝑝 = 𝑛𝑖 𝑅=

𝑅 =

+ 𝑛𝑖 2

;and 𝑝 =

10×10−4

(𝑛𝑜𝑡𝑒: 𝑁𝐷 𝜇𝑛 ≫

𝑛𝑖 2 𝜌𝐿 𝐿 𝑅 = = = 𝑁𝐷 𝐴 𝜎𝐴 𝑛𝑖 2 𝜇 ) 𝑁𝐷 𝑝

𝑁𝐴 −𝑁 𝐷 2

𝑅=

𝑁𝐴 −𝑁𝐷 2 ) 2

+ 𝑛𝑖 2

= 7.58 × 109 Ω = 7.59 GΩ 𝐿

𝑛 𝑞 (𝑁𝐷 𝜇𝑛 + 𝑁𝑖 𝜇𝑝 ) 𝐴 𝐷 2

≈

𝐿 𝑞(𝑁𝐷 𝜇𝑛 )𝐴

10 × 10 −4 = 17361 Ω = 17.361 𝑘Ω 1.602 × 10 −19 × 1 × 1016 × 1200 × 3 × 10−4 × 1 × 10−4

𝑑) 𝑆𝑖𝑛𝑐𝑒 𝑁𝐴 is comparable to 𝑛𝑖 , 𝑝=

+ √(

𝐿 𝐿 𝐿 𝜌𝐿 = = = 𝐴 𝜎𝐴 [𝑞(𝑛𝜇𝑛 + 𝑝𝜇𝑝 )]𝐴 [𝑞𝑛𝑖 (𝜇𝑛 + 𝜇𝑝 )]𝐴

1.602×10−19 ×1.5×1010 (1350+480)×3×10−4 ×1×10−4

𝑏) 𝑛 = 𝑁𝐷 ; 𝑝 =

𝑅=

𝑁𝐷 −𝑁𝐴 2 ) 2

𝑁𝐴 − 𝑁𝐷 𝑁𝐴 − 𝑁𝐷 2 + √( ) + 𝑛𝑖 2 = 2.08 × 1010 𝑐𝑚−3 ; 2 2 𝜌𝐿 𝐿 𝐿 = = 𝐴 𝜎𝐴 𝑞(𝑛𝜇𝑛 + 𝑝𝜇𝑝 )𝐴

𝑛=

𝑛𝑖 2 = 1.08 × 1010 𝑐𝑚−3 𝑝

10 × 10 −4 𝑅 = 1.602 × 10 −19(2.08 × 1010 × 480 + 1.08 × 1010 × 1200 ) × 3 × 10−4 × 1 × 10 −4 = 9.07 𝐺Ω 𝑒) 𝑅 =

𝜌𝐿 𝐴

=

2.8 × 10 −6 × 10 × 10−4 = 0.0934 Ω = 93.4 𝑚Ω 3 × 10 −4 × 1 × 10−4

3.108) Holes are being steadily injected into a region of n-type silicon. In the Steady state, the excess-hole concentration profile shown in Fig P3.108 Is established in the n-type silicon region. Here “excess” means over and above the concentration pno. If ND = 1016 /𝑐𝑚3 , ni = 1.5 × 1010 /𝑐𝑚3 and W = 5m,

find the density of the current that will flow in the x direction.

𝐽𝑝 = −𝑞𝐷𝑝 𝑝𝑛𝑜 =

𝑛𝑖 2

𝑛𝑛𝑜

𝑑𝑝 𝑑𝑥

=

𝑛𝑖 2

𝑁𝐷

=

(1.5 × 1010)2 = 2.25 × 104 𝑐𝑚−3 1016

𝑝𝑛𝑜 − 1000𝑝𝑛𝑜 −999𝑝𝑛𝑜 −999 × 2.25 × 104 𝑑𝑝 = = = = −4.4955 × 1010 𝑐𝑚−4 𝑑𝑥 𝑊−0 𝑊 5 × 10−4 𝐽𝑝 = −𝑞𝐷𝑝

𝑑𝑝 = −1.602 × 10 −19 × 12 × (−4.4955 × 1010) = 8.64 × 10−8 𝐴/𝑐𝑚2 𝑑𝑥

3.115) If for a particular junction, the acceptor concentration is 1 × 1016/cm3 and the donor concentration is 1 × 1015/cm3, find the junction built-in voltage (barrier voltage). Assume ni = 1 × 1010/cm3. Also, find Wdep and its extent in each of the p and n regions when the junction is reverse biased with VR = 5 V. At this value of the reverse bias, calculate the magnitude of the charge stored on either side of the junction. Assume the junction area is 400 m2. Also, calculate Cj.

𝑉𝑂 = V𝑇 × ln

𝑁𝐴 × 𝑁𝐷 𝑛𝑖 2

𝑉𝑂 = 0.0258 × ln

𝑉𝑂 = 0.653 𝑉 𝑊𝑑𝑒𝑝 = √ 𝑊𝑑𝑒𝑝 = √

1016 × 1015 (1010)2

2𝜀𝑠 1 1 )(𝑉𝑂 + 𝑉𝑅 ) ( + 𝑞 𝑁𝐴 𝑁𝐷

2×11.7×8.854×10−14 1.602×10−19

1

( 1016 +

1

1015

𝑊𝑑𝑒𝑝 = 𝑥𝑝 + 𝑥𝑛 → 𝑥𝑝 + 𝑥𝑛 = 2.836

) (0.653 + 5)

;

𝑥𝑝

𝑥𝑛

= 2.836 × 10−4 cm = 2.836 m =

𝑁𝐷 𝑁𝐴

→

𝑥𝑝

𝑥𝑛

=

1015

1016

→

𝑥𝑛 𝑥𝑝

= 10

Solving and simultaneously yields: 𝑥𝑝 =

2.836 11

= 0.258 m

and 𝑥𝑛 = 2.578 m

𝑞𝑗 = 𝑞𝑁𝐷 𝑥𝑛 𝐴 = 𝑞𝑁𝐴 𝑥𝑝 𝐴 = 1.602 × 10−19 × 1016 × 0.2578 × 10−4 × 400 × 10−8 = 1.652 × 10−13 𝐶 𝐶𝑗 =

𝜀𝑠 × 𝐴 11.7 × 8.854 × 10−14 × 400 × 10 −8 = = 1.461 × 10−14 𝐹 = 14.61 𝑓𝐹 𝑊𝑑𝑒𝑝 2.836 × 10−4

3.121) A p+-n diode is one in which the doping concentration in the p region is much greater than that in the n region. In such a diode, the forward current is mostly due to the hole injection across the junction. Show that: 𝐼 𝐼𝑝 = 𝐴𝑞𝑛𝑖 2 (

𝑉 𝐷𝑝 ) (𝑒 𝑉𝑇 − 1) 𝐿𝑝 𝑁𝐷

For the specific case in which 𝑁𝐷 = 5 × 1016/𝑐𝑚3 , 𝐷𝑝 = 10 𝑐𝑚2 /𝑠, 𝜏𝑝 = 0.1 𝑠, and 𝐴 = 104 𝑚2 , find 𝐼𝑆 and the voltage 𝑉 obtained when 𝐼 = 0.2 𝑚𝐴. Assume operation at 300 K where 𝑛𝑖 = 1.5 × 1010 /𝑐𝑚3 . Also, calculate the excess minority-carrier charge and the value of the diffusion capacitance at 𝐼 = 0.2 𝑚𝐴. 𝑉

𝐼 = 𝐼𝑆 (𝑒 𝑉𝑇 − 1) = 𝐼𝑝 + 𝐼𝑛

Where 𝐼𝑆 = 𝐴𝑞𝑛𝑖 2 (

𝐷𝑝

𝐿𝑝 𝑁𝐷

+

𝐷𝑛 ) 𝐿𝑛 𝑁𝐴

𝐼 = 𝐴𝑞𝑛𝑖 2 (

𝐷𝑝

𝐿𝑝 𝑁𝐷

+

𝑉

𝐷𝑛 ) (𝑒 𝑉𝑇 𝐿𝑛 𝑁𝐴

− 1)

𝐼𝑝 = 𝐴𝑞𝑛𝑖 2 (

𝑉 𝑉 𝐷𝑝 𝐷𝑛 ) (𝑒 𝑉𝑇 − 1) ) (𝑒 𝑉𝑇 − 1) 𝑎𝑛𝑑 𝐼𝑛 = 𝐴𝑞𝑛𝑖 2 ( 𝐿𝑛 𝑁𝐴 𝐿𝑝 𝑁𝐷

𝐼𝑝 = 𝐴𝑞𝑛𝑖 2 (

𝑉 𝐷𝑝 ) (𝑒 𝑉𝑇 − 1) ≈ 𝐼 = 0.2 𝑚𝐴 𝐿𝑝 𝑁𝐷

∵ the junction is p+-n 𝑁𝐴 ≫ 𝑁𝐷 𝐼𝑝 ≫ 𝐼𝑛 𝐼 ≈ 𝐼𝑝

𝐿𝑝 = √𝐷𝑝 𝜏𝑝 = √10 × 0.1 × 10−6 = 1 × 10−3 𝑐𝑚

𝐼𝑆 ≈ 𝐴𝑞𝑛𝑖 2 ( 𝑉 ≈ 𝑉𝑇 ln(

𝐷𝑝 10 ) = 104 × 10−8 × 1.602−19 × (1.5 × 1010 )2 = 0.72 × 10−15 𝐴 −3 𝐿𝑝 𝑁𝐷 1 × 10 × 5 × 1016

𝐼𝑝 + 1) = 0.0258 × 26.35 = 0.6798 𝑉 𝐼𝑆

𝑄𝑝 = 𝜏𝑝 𝐼𝑝 = 0.1 × 10 −6 × 0.2 × 10−3 = 2 × 10 −11 𝐶 = 20 𝑝𝐶 𝐶𝑑 =

𝑄𝑝 + 𝑄𝑛 𝑄𝑝 𝜏𝑝 𝐼𝑝 𝑄 = ≈ = 7.752 × 10−10 = 0.7752 𝑛𝐹 = 𝑉𝑇 𝑉𝑇 𝑉𝑇 𝑉𝑇...

Similar Free PDFs

Engineering Eco. Course Outline

- 5 Pages

Mechanical-engineering

- 1 Pages

Mechanical engineering

- 1 Pages

2019-2020 Mechanical Engineering

- 2 Pages

Mechanical Engineering Circuits

- 10 Pages

MECHANICAL ENGINEERING REVIEW MANUAL

- 509 Pages

Mechanical engineering lab report

- 18 Pages

Mechanical Engineering Lecture Notes

- 13 Pages

MECHANICAL ENGINEERING REVIEW MANUAL

- 509 Pages

Mechanical Engineering Elements

- 29 Pages

Mechanical engineering design

- 6 Pages

Mechanical Engineering Solutions

- 21 Pages

Mechanical Engineering Level M

- 16 Pages

Popular Institutions

- Tinajero National High School - Annex

- Politeknik Caltex Riau

- Yokohama City University

- SGT University

- University of Al-Qadisiyah

- Divine Word College of Vigan

- Techniek College Rotterdam

- Universidade de Santiago

- Universiti Teknologi MARA Cawangan Johor Kampus Pasir Gudang

- Poltekkes Kemenkes Yogyakarta

- Baguio City National High School

- Colegio san marcos

- preparatoria uno

- Centro de Bachillerato Tecnológico Industrial y de Servicios No. 107

- Dalian Maritime University

- Quang Trung Secondary School

- Colegio Tecnológico en Informática

- Corporación Regional de Educación Superior

- Grupo CEDVA

- Dar Al Uloom University

- Centro de Estudios Preuniversitarios de la Universidad Nacional de Ingeniería

- 上智大学

- Aakash International School, Nuna Majara

- San Felipe Neri Catholic School

- Kang Chiao International School - New Taipei City

- Misamis Occidental National High School

- Institución Educativa Escuela Normal Juan Ladrilleros

- Kolehiyo ng Pantukan

- Batanes State College

- Instituto Continental

- Sekolah Menengah Kejuruan Kesehatan Kaltara (Tarakan)

- Colegio de La Inmaculada Concepcion - Cebu